How to use has_feature method in lisa

Best Python code snippet using lisa_python

ioi_models.py

Source: ioi_models.py

...87 aparts = features[0].feature.split('.')88 # tile_name = aparts[0]89 ioi_site = get_ioi_site(top.db, top.grid, aparts[0], aparts[1])90 site = Site(features, ioi_site)91 if site.has_feature("IN_USE") and (site.has_feature("IDELAY_VALUE")92 or site.has_feature("ZIDELAY_VALUE")):93 bel = Bel('IDELAYE2')94 bel.set_bel('IDELAYE2')95 bel.parameters['REFCLK_FREQUENCY'] = "200.0"96 if site.has_feature("CINVCTRL_SEL"):97 bel.parameters["CINVCTRL_SEL"] = '"TRUE"'98 if site.has_feature("PIPE_SEL"):99 bel.parameters['PIPE_SEL'] = '"TRUE"'100 if site.has_feature("HIGH_PERFORMANCE_MODE"):101 bel.parameters['HIGH_PERFORMANCE_MODE'] = '"TRUE"'102 if site.has_feature("DELAY_SRC_DATAIN"):103 bel.parameters['DELAY_SRC'] = '"DATAIN"'104 else:105 bel.parameters['DELAY_SRC'] = '"IDATAIN"'106 if site.has_feature("IS_DATAIN_INVERTED"):107 bel.parameters['IS_DATAIN_INVERTED'] = 1108 site_pips = make_inverter_path('DATAIN', 1)109 else:110 site_pips = make_inverter_path('DATAIN', 0)111 site.add_sink(112 bel, 'DATAIN', 'DATAIN', bel.bel, 'DATAIN', site_pips=site_pips)113 if site.has_feature("IS_IDATAIN_INVERTED"):114 bel.parameters['IS_IDATAIN_INVERTED'] = 1115 site_pips = make_inverter_path('IDATAIN', 1)116 else:117 site_pips = make_inverter_path('IDATAIN', 0)118 site.add_sink(119 bel, 'IDATAIN', 'IDATAIN', bel.bel, 'IDATAIN', site_pips=site_pips)120 if site.has_feature("IDELAY_VALUE"):121 idelay_value = site.decode_multi_bit_feature('IDELAY_VALUE')122 bel.parameters['IDELAY_VALUE'] = str(idelay_value)123 else:124 bel.parameters['IDELAY_VALUE'] = '0'125 if site.has_feature("IDELAY_TYPE_VARIABLE"):126 bel.parameters['IDELAY_TYPE'] = '"VARIABLE"'127 elif site.has_feature("IDELAY_TYPE_VAR_LOAD"):128 bel.parameters['IDELAY_TYPE'] = '"VAR_LOAD"'129 else:130 bel.parameters['IDELAY_TYPE'] = '"FIXED"'131 # Adding sinks132 for wire in ('C', 'CE', 'CINVCTRL', 'INC', 'LD', 'LDPIPEEN', 'REGRST'):133 site.add_sink(bel, wire, wire, bel.bel, wire)134 # Adding sources135 site.add_source(bel, 'DATAOUT', 'DATAOUT', bel.bel, 'DATAOUT')136 bel.add_unconnected_port('CNTVALUEIN', 5, direction="input")137 bel.add_unconnected_port('CNTVALUEOUT', 5, direction="output")138 for i in range(5):139 bel.map_bel_pin_to_cell_pin(140 bel_name=bel.bel,141 bel_pin='CNTVALUEIN{}'.format(i),142 cell_pin='CNTVALUEIN[{}]'.format(i))143 bel.map_bel_pin_to_cell_pin(144 bel_name=bel.bel,145 bel_pin='CNTVALUEOUT{}'.format(i),146 cell_pin='CNTVALUEOUT[{}]'.format(i))147 site.add_bel(bel)148 # TODO: handle CNTVALUEIN and CNTVALUEOUT149 top.add_site(site)150def process_iserdes(top, site, idelay_site=None):151 """152 Decodes the ISERDES primitive153 """154 # ISERDES155 bel = Bel('ISERDESE2')156 bel.set_bel('ISERDESE2')157 site.override_site_type('ISERDESE2')158 # Data rate, data width and interface type159 config_features = {160 "ISERDES.MEMORY.DDR.W4",161 "ISERDES.MEMORY_DDR3.DDR.W4",162 "ISERDES.MEMORY_QDR.DDR.W4",163 "ISERDES.NETWORKING.SDR.W2",164 "ISERDES.NETWORKING.SDR.W3",165 "ISERDES.NETWORKING.SDR.W4",166 "ISERDES.NETWORKING.SDR.W5",167 "ISERDES.NETWORKING.SDR.W6",168 "ISERDES.NETWORKING.SDR.W7",169 "ISERDES.NETWORKING.SDR.W8",170 "ISERDES.NETWORKING.DDR.W4",171 "ISERDES.NETWORKING.DDR.W6",172 "ISERDES.NETWORKING.DDR.W8",173 "ISERDES.NETWORKING.DDR.W10",174 "ISERDES.NETWORKING.DDR.W14",175 "ISERDES.OVERSAMPLE.DDR.W4",176 }177 # Isolate config features, only one of them can be set.178 set_features = set([f.feature for f in site.set_features if f.value])179 set_config_features = set_features & config_features180 assert len(set_config_features) == 1, set_config_features181 # Decode182 feature = next(iter(set_config_features))183 parts = feature.split(".")184 bel.parameters['INTERFACE_TYPE'] = '"{}"'.format(parts[1])185 bel.parameters['DATA_RATE'] = '"{}"'.format(parts[2])186 bel.parameters['DATA_WIDTH'] = int(parts[3][1:])187 site.add_source(bel, 'O', 'O', bel.bel, 'O')188 if site.has_feature('IFF.ZINV_C'):189 bel.parameters['IS_CLK_INVERTED'] = 0190 bel.parameters['IS_CLKB_INVERTED'] = 1191 else:192 bel.parameters['IS_CLK_INVERTED'] = 1193 bel.parameters['IS_CLKB_INVERTED'] = 0194 site.add_sink(195 bel,196 'CLK',197 'CLK',198 bel.bel,199 'CLK',200 site_pips=make_inverter_path('CLK', bel.parameters['IS_CLK_INVERTED']))201 site.add_sink(202 bel,203 'CLKB',204 'CLKB',205 bel.bel,206 'CLKB',207 site_pips=make_inverter_path('CLKB',208 bel.parameters['IS_CLKB_INVERTED']))209 site.add_sink(bel, 'CLKDIV', 'CLKDIV', bel.bel, 'CLKDIV')210 site.add_sink(bel, 'RST', 'SR', bel.bel, 'RST', sink_site_type_pin='RST')211 if site.has_feature('ZINV_D'):212 bel.parameters['IS_D_INVERTED'] = 0213 else:214 bel.parameters['IS_D_INVERTED'] = 1215 num_ce = None216 if site.has_feature('ISERDES.NUM_CE.N2'):217 num_ce = 2218 else:219 num_ce = 1220 bel.parameters['NUM_CE'] = num_ce221 if site.has_feature('IDELMUXE3.P0') and site.has_feature('IFFDELMUXE3.P0'):222 bel.parameters['IOBDELAY'] = '"BOTH"'223 elif site.has_feature('IFFDELMUXE3.P0'):224 bel.parameters['IOBDELAY'] = '"IFD"'225 elif site.has_feature('IDELMUXE3.P0'):226 bel.parameters['IOBDELAY'] = '"IBUF"'227 site.add_sink(bel, 'CE1', 'CE1', bel.bel, 'CE1')228 site.add_sink(bel, 'CE2', 'CE2', bel.bel, 'CE2')229 site.add_sink(bel, 'BITSLIP', 'BITSLIP', bel.bel, 'BITSLIP')230 site.add_sink(bel, 'DYNCLKDIVSEL', 'DYNCLKDIVSEL', bel.bel, 'DYNCLKDIVSEL')231 site.add_sink(bel, 'DYNCLKSEL', 'DYNCLKSEL', bel.bel, 'DYNCLKSEL')232 if idelay_site and idelay_site.has_feature("IN_USE") and (233 idelay_site.has_feature("IDELAY_VALUE")234 or idelay_site.has_feature("ZIDELAY_VALUE")):235 site.add_sink(bel, 'DDLY', 'DDLY', bel.bel, 'DDLY')236 bel.add_unconnected_port('D', None, direction="input")237 bel.map_bel_pin_to_cell_pin(bel.bel, 'D', 'D')238 else:239 site.add_sink(240 bel,241 'D',242 'D',243 bel.bel,244 'D',245 site_pips=make_inverter_path('D', bel.parameters['IS_D_INVERTED']))246 bel.add_unconnected_port('DDLY', None, direction="input")247 bel.map_bel_pin_to_cell_pin(bel.bel, 'DDLY', 'DDLY')248 for i in range(1, 9):249 port_q = 'Q{}'.format(i)250 site.add_source(bel, port_q, port_q, bel.bel, port_q)251 for idx in range(1, 5):252 bel.parameters['SRVAL_Q{}'.format(idx)] = "0" if site.has_feature(253 'IFF.ZSRVAL_Q{}'.format(idx)) else "1"254 bel.parameters['INIT_Q{}'.format(idx)] = "0" if site.has_feature(255 'IFF.ZINIT_Q{}'.format(idx)) else "1"256 for unused_in in [257 'SHIFTIN1', 'SHIFTIN2', 'OFB', 'OCLK', 'OCLKB', 'CLKDIVP'258 ]:259 bel.add_unconnected_port(unused_in, None, direction="input")260 bel.map_bel_pin_to_cell_pin(bel.bel, unused_in, unused_in)261 for unused_out in ['SHIFTOUT1', 'SHIFTOUT2']:262 bel.add_unconnected_port(unused_out, None, direction="output")263 bel.map_bel_pin_to_cell_pin(bel.bel, unused_out, unused_out)264 site.add_bel(bel)265def process_iddr(top, site, idelay_site=None):266 """267 Decodes the IDDR primitive268 """269 # IDDR. At this point we can't tell if it is IDDR or IDDR_2CLK so the270 # more generic one is instanced.271 bel = Bel('IDDR_2CLK')272 bel.set_bel('IFF')273 site.add_sink(bel, 'CE', 'CE1', bel.bel, 'CE')274 site.add_source(bel, 'Q1', 'Q1', bel.bel, 'Q1')275 site.add_source(bel, 'Q2', 'Q2', bel.bel, 'Q2')276 if idelay_site and idelay_site.has_feature("IN_USE") and (277 idelay_site.has_feature("IDELAY_VALUE")278 or idelay_site.has_feature("ZIDELAY_VALUE")):279 site.add_sink(bel, 'D', 'DDLY', bel.bel, 'D')280 else:281 site.add_sink(bel, 'D', 'D', bel.bel, 'D')282 # Determine whether we have SET or RESET283 assert site.has_feature('IFF.ZSRVAL_Q1') == site.has_feature(284 'IFF.ZSRVAL_Q2'), (site.tile, site.site)285 if site.has_feature('IFF.ZSRVAL_Q1'):286 site.add_sink(bel, 'R', 'SR', bel.bel, 'SR')287 else:288 site.add_sink(bel, 'S', 'SR', bel.bel, 'SR')289 if site.has_feature('IFF.DDR_CLK_EDGE.SAME_EDGE'):290 bel.parameters['DDR_CLK_EDGE'] = '"SAME_EDGE"'291 elif site.has_feature('IFF.DDR_CLK_EDGE.OPPOSITE_EDGE'):292 bel.parameters['DDR_CLK_EDGE'] = '"OPPOSITE_EDGE"'293 else:294 bel.parameters['DDR_CLK_EDGE'] = '"SAME_EDGE_PIPELINED"'295 # INIT296 for q in ['Q1', 'Q2']:297 if site.has_feature('IFF.ZINIT_' + q):298 bel.parameters['INIT_' + q] = "1'b0"299 else:300 bel.parameters['INIT_' + q] = "1'b1"301 # SRTYPE302 if site.has_feature('IFF.SRTYPE.SYNC'):303 bel.parameters['SRTYPE'] = '"SYNC"'304 else:305 bel.parameters['SRTYPE'] = '"ASYNC"'306 # IS_C_INVERTED307 c_inverted = site.has_feature('IFF.ZINV_C')308 if site.has_feature('IFF.ZINV_C'):309 bel.parameters['IS_C_INVERTED'] = "1'b0"310 else:311 bel.parameters['IS_C_INVERTED'] = "1'b1"312 site.add_sink(313 bel,314 'C',315 'CLK',316 bel.bel,317 'CK',318 site_pips=make_inverter_path('CLK', c_inverted))319 site.add_sink(320 bel,321 'CB',322 'CLKB',323 bel.bel,324 'CKB',325 site_pips=make_inverter_path('CLKB', False))326 # IS_CB_INVERTED327 # There seem not to be any bits for this one...328 # IS_D_INVERTED329 if site.has_feature('ZINV_D'):330 bel.parameters['IS_D_INVERTED'] = "1'b0"331 else:332 bel.parameters['IS_D_INVERTED'] = "1'b1"333 site.add_bel(bel, name="IDDR")334def process_ilogic_idelay(top, features):335 """336 Processes the ILOGIC and IDELAY sites.337 """338 ilogic_features = features['ILOGIC']339 idelay_features = features['IDELAY']340 ilogic_aparts = ilogic_features[0].feature.split('.')341 idelay_aparts = idelay_features[0].feature.split('.')342 # tile_name = aparts[0]343 ioi_ilogic_site = get_ioi_site(top.db, top.grid, ilogic_aparts[0],344 ilogic_aparts[1])345 ioi_idelay_site = get_ioi_site(top.db, top.grid, idelay_aparts[0],346 idelay_aparts[1])347 site = Site(ilogic_features, ioi_ilogic_site)348 # Get idelay site corresponding to this tile and check if it is used349 idelay_site = None350 add_site = False351 if len(idelay_features):352 idelay_site = Site(idelay_features, ioi_idelay_site)353 # ILOGICE3 in ISERDES mode354 if site.has_feature("ISERDES.IN_USE") and site.has_feature(355 "IDDR_OR_ISERDES.IN_USE"):356 process_iserdes(top, site, idelay_site)357 add_site = True358 # ILOGICE3 in IDDR mode359 elif site.has_feature("IDDR_OR_ISERDES.IN_USE"):360 process_iddr(top, site, idelay_site)361 add_site = True362 # Passthrough363 elif site.has_feature("ZINV_D"):364 site.sources['O'] = None365 site.sinks['D'] = []366 site.outputs['O'] = 'D'367 add_site = True368 if add_site:369 site.set_post_route_cleanup_function(cleanup_ilogic)370 top.add_site(site)371# =============================================================================372def process_oddr_oq(top, site):373 """374 Decodes the ODDR primitive driving OQ (data) signal375 """376 # ODDR377 bel = Bel('ODDR', name='ODDR_OQ')378 bel.set_bel('OUTFF')379 site.add_sink(bel, 'C', 'CLK', bel.bel, 'CK')380 site.add_sink(bel, 'CE', 'OCE', bel.bel, 'CE')381 site.add_sink(bel, 'D1', 'D1', bel.bel, 'D1')382 site.add_sink(bel, 'D2', 'D2', bel.bel, 'D2')383 site.add_source(bel, 'Q', 'OQ', bel.bel, 'Q')384 # Determine whether we have SET or RESET385 if site.has_feature('ZSRVAL_OQ'):386 site.add_sink(bel, 'R', 'SR', bel.bel, 'SR')387 bel.add_unconnected_port('S', None, direction="input")388 else:389 site.add_sink(bel, 'S', 'SR', bel.bel, 'SR')390 bel.add_unconnected_port('R', None, direction="input")391 # DDR_CLK_EDGE392 if site.has_feature('ODDR.DDR_CLK_EDGE.SAME_EDGE'):393 bel.parameters['DDR_CLK_EDGE'] = '"SAME_EDGE"'394 else:395 bel.parameters['DDR_CLK_EDGE'] = '"OPPOSITE_EDGE"'396 # INIT397 if site.has_feature('ZINIT_OQ'):398 bel.parameters['INIT'] = "1'b0"399 else:400 bel.parameters['INIT'] = "1'b1"401 # SRTYPE402 if site.has_feature('OSERDES.SRTYPE.SYNC'):403 bel.parameters['SRTYPE'] = '"SYNC"'404 else:405 bel.parameters['SRTYPE'] = '"ASYNC"'406 # IS_C_INVERTED407 if site.has_feature('ZINV_CLK'):408 bel.parameters['IS_C_INVERTED'] = "1'b0"409 else:410 bel.parameters['IS_C_INVERTED'] = "1'b1"411 # IS_D1_INVERTED412 if site.has_feature('IS_D1_INVERTED'):413 bel.parameters['IS_D1_INVERTED'] = "1'b1"414 else:415 bel.parameters['IS_D1_INVERTED'] = "1'b0"416 # IS_D2_INVERTED417 if site.has_feature('IS_D2_INVERTED'):418 bel.parameters['IS_D2_INVERTED'] = "1'b1"419 else:420 bel.parameters['IS_D2_INVERTED'] = "1'b0"421 site.add_bel(bel, name="ODDR_OQ")422def process_oddr_tq(top, site):423 """424 Decodes the ODDR primitive driving TQ (tri-state) signal425 """426 # ODDR427 bel = Bel('ODDR', name='ODDR_TQ')428 bel.set_bel('TFF')429 site.add_sink(bel, 'C', 'CLK', bel.bel, 'CK')430 site.add_sink(bel, 'CE', 'TCE', bel.bel, 'CE')431 site.add_sink(bel, 'D1', 'T1', bel.bel, 'D1')432 site.add_sink(bel, 'D2', 'T2', bel.bel, 'D2')433 site.add_source(bel, 'Q', 'TQ', bel.bel, 'Q')434 # Determine whether we have SET or RESET435 if site.has_feature('ZSRVAL_TQ'):436 site.add_sink(bel, 'R', 'SR', bel.bel, 'SR')437 else:438 site.add_sink(bel, 'S', 'SR', bel.bel, 'SR')439 # DDR_CLK_EDGE440 if site.has_feature('ODDR.DDR_CLK_EDGE.SAME_EDGE'):441 bel.parameters['DDR_CLK_EDGE'] = '"SAME_EDGE"'442 else:443 bel.parameters['DDR_CLK_EDGE'] = '"OPPOSITE_EDGE"'444 # INIT445 if site.has_feature('ZINIT_TQ'):446 bel.parameters['INIT'] = "1'b0"447 else:448 bel.parameters['INIT'] = "1'b1"449 # SRTYPE450 if site.has_feature('OSERDES.TSRTYPE.SYNC'):451 bel.parameters['SRTYPE'] = '"SYNC"'452 else:453 bel.parameters['SRTYPE'] = '"ASYNC"'454 # IS_C_INVERTED455 if site.has_feature('ZINV_CLK'):456 bel.parameters['IS_C_INVERTED'] = "1'b0"457 else:458 bel.parameters['IS_C_INVERTED'] = "1'b1"459 # IS_D1_INVERTED460 if site.has_feature('ZINV_T1'):461 bel.parameters['IS_D1_INVERTED'] = "1'b0"462 else:463 bel.parameters['IS_D1_INVERTED'] = "1'b1"464 # IS_D2_INVERTED465 if site.has_feature('ZINV_T2'):466 bel.parameters['IS_D2_INVERTED'] = "1'b0"467 else:468 bel.parameters['IS_D2_INVERTED'] = "1'b1"469 site.add_bel(bel, name="ODDR_TQ")470def process_oserdes(top, site):471 """472 Decodes the OSERDESE2 primitive473 """474 # OSERDES475 bel = Bel('OSERDESE2')476 site.override_site_type('OSERDESE2')477 bel.set_bel('OSERDESE2')478 data_rate_oq = None479 if site.has_feature("OSERDES.DATA_RATE_OQ.DDR"):480 data_rate_oq = '"DDR"'481 elif site.has_feature("OSERDES.DATA_RATE_OQ.SDR"):482 data_rate_oq = '"SDR"'483 else:484 assert False485 bel.parameters['DATA_RATE_OQ'] = data_rate_oq486 data_rate_tq = None487 if site.has_feature("OSERDES.DATA_RATE_TQ.DDR"):488 data_rate_tq = '"DDR"'489 elif site.has_feature("OSERDES.DATA_RATE_TQ.SDR"):490 data_rate_tq = '"SDR"'491 elif site.has_feature("OSERDES.DATA_RATE_TQ.BUF"):492 data_rate_tq = '"BUF"'493 else:494 assert False495 bel.parameters['DATA_RATE_TQ'] = data_rate_tq496 data_width = None497 if site.has_feature("OSERDES.DATA_WIDTH.SDR.W2"):498 expect_data_rate = 'SDR'499 data_width = 2500 elif site.has_feature("OSERDES.DATA_WIDTH.SDR.W3"):501 expect_data_rate = 'SDR'502 data_width = 3503 elif site.has_feature("OSERDES.DATA_WIDTH.SDR.W4"):504 expect_data_rate = 'SDR'505 data_width = 4506 elif site.has_feature("OSERDES.DATA_WIDTH.SDR.W5"):507 expect_data_rate = 'SDR'508 data_width = 5509 elif site.has_feature("OSERDES.DATA_WIDTH.SDR.W6"):510 expect_data_rate = 'SDR'511 data_width = 6512 elif site.has_feature("OSERDES.DATA_WIDTH.SDR.W7"):513 expect_data_rate = 'SDR'514 data_width = 7515 elif site.has_feature("OSERDES.DATA_WIDTH.SDR.W8"):516 expect_data_rate = 'SDR'517 data_width = 8518 elif site.has_feature("OSERDES.DATA_WIDTH.DDR.W4"):519 expect_data_rate = 'DDR'520 data_width = 4521 elif site.has_feature("OSERDES.DATA_WIDTH.DDR.W6"):522 expect_data_rate = 'DDR'523 data_width = 6524 elif site.has_feature("OSERDES.DATA_WIDTH.DDR.W8"):525 expect_data_rate = 'DDR'526 data_width = 8527 else:528 assert False529 if expect_data_rate == 'SDR':530 assert site.has_feature("OSERDES.DATA_RATE_OQ.SDR")531 elif expect_data_rate == 'DDR':532 assert site.has_feature("OSERDES.DATA_RATE_OQ.DDR")533 else:534 assert False535 bel.parameters['DATA_WIDTH'] = data_width536 bel.parameters['TRISTATE_WIDTH'] = "4" if site.has_feature(537 "OSERDES.TRISTATE_WIDTH.W4") else "1"538 bel.parameters['SERDES_MODE'] = '"SLAVE"' if site.has_feature(539 "OSERES.SERDES_MODE.SLAVE") else '"MASTER"'540 site.add_source(bel, 'OQ', 'OQ', bel.bel, 'OQ')541 site.add_source(bel, 'TQ', 'TQ', bel.bel, 'TQ')542 site.add_sink(bel, 'CLK', 'CLK', bel.bel, 'CLK')543 site.add_sink(bel, 'CLKDIV', 'CLKDIV', bel.bel, 'CLKDIV')544 for i in range(1, 9):545 inverted = "IS_D{}_INVERTED".format(i)546 d_inverted = site.has_feature(inverted)547 if d_inverted:548 bel.parameters[inverted] = 1549 wire = 'D{}'.format(i)550 site_pips = make_inverter_path(wire, d_inverted)551 site.add_sink(bel, wire, wire, bel.bel, wire, site_pips=site_pips)552 for i in range(1, 5):553 t_inverted = not site.has_feature("ZINV_T{}".format(i))554 if t_inverted:555 bel.parameters["IS_T{}_INVERTED".format(i)] = 1556 wire = 'T{}'.format(i)557 site_pips = make_inverter_path(wire, t_inverted)558 site.add_sink(bel, wire, wire, bel.bel, wire, site_pips=site_pips)559 site.add_sink(bel, 'OCE', 'OCE', bel.bel, 'OCE')560 site.add_sink(bel, 'TCE', 'TCE', bel.bel, 'TCE')561 site.add_sink(bel, 'RST', 'SR', bel.bel, 'RST', sink_site_type_pin='RST')562 bel.parameters["INIT_OQ"] = "0" if site.has_feature('ZINIT_OQ') else "1"563 bel.parameters["INIT_TQ"] = "0" if site.has_feature('ZINIT_TQ') else "1"564 bel.parameters["SRVAL_OQ"] = "0" if site.has_feature('ZSRVAL_OQ') else "1"565 bel.parameters["SRVAL_TQ"] = "0" if site.has_feature('ZSRVAL_TQ') else "1"566 for unused_in in ['SHIFTIN1', 'SHIFTIN2', 'TBYTEIN']:567 bel.add_unconnected_port(unused_in, None, direction="input")568 bel.map_bel_pin_to_cell_pin(bel.bel, unused_in, unused_in)569 for unused_out in ['SHIFTOUT1', 'SHIFTOUT2', 'TBYTEOUT', 'OFB', 'TFB']:570 bel.add_unconnected_port(unused_out, None, direction="output")571 bel.map_bel_pin_to_cell_pin(bel.bel, unused_out, unused_out)572 site.add_bel(bel)573def process_ologic(top, features):574 """575 Processes the OLOGICE2 site576 """577 aparts = features[0].feature.split('.')578 # tile_name = aparts[0]579 ioi_site = get_ioi_site(top.db, top.grid, aparts[0], aparts[1])580 site = Site(features, ioi_site)581 # OLOGICE2 in OSERDES mode582 if site.has_feature("OSERDES.IN_USE"):583 process_oserdes(top, site)584 # OLOGICE2 with ODDRs or passtrhough585 else:586 # ODDR for OQ used587 if not site.has_feature("OMUX.D1"):588 process_oddr_oq(top, site)589 # Passthrough590 else:591 site.sources['OQ'] = None592 site.sinks['D1'] = []593 site.outputs['OQ'] = 'D1'594 # ODDR for TQ used595 if not site.has_feature("OSERDES.DATA_RATE_TQ.BUF"):596 process_oddr_tq(top, site)597 # Passthrough598 else:599 site.sources['TQ'] = None600 site.sinks['T1'] = []601 site.outputs['TQ'] = 'T1'602 top.add_site(site)603# =============================================================================604def process_ioi(conn, top, tile, features):605 ilogic_idelay = {606 "0": {607 'ILOGIC': [],608 'IDELAY': []609 },...stats.py

Source: stats.py

...100 # Check for proficiency101 is_proficient = self.skill_name in character.skill_proficiencies102 if is_proficient:103 modifier += character.proficiency_bonus104 elif character.has_feature(JackOfAllTrades):105 modifier += character.proficiency_bonus // 2106 elif character.has_feature(RemarkableAthelete):107 if self.ability_name.lower() in ('strength',108 'dexterity', 'constitution'):109 modifier += ceil(character.proficienc_bonus / 2.)110 111 # Check for expertise112 is_expert = self.skill_name in character.skill_expertise113 if is_expert:114 modifier += character.proficiency_bonus115 return modifier116class ArmorClass():117 """118 The Armor Class of a character119 """120 def __get__(self, char, Character):121 armor = char.armor or NoArmor()122 ac = armor.base_armor_class123 # calculate and apply modifiers124 if armor.dexterity_mod_max is None:125 ac += char.dexterity.modifier126 else:127 ac += min(char.dexterity.modifier, armor.dexterity_mod_max)128 if char.has_feature(NaturalArmor):129 ac = max(ac, 13 + char.dexterity.modifier)130 shield = char.shield or NoShield()131 ac += shield.base_armor_class132 # Compute feature-specific additions133 if char.has_feature(UnarmoredDefenseMonk):134 if (isinstance(armor, NoArmor) and isinstance(shield, NoShield)):135 ac += char.wisdom.modifier136 if char.has_feature(UnarmoredDefenseBarbarian):137 if isinstance(armor, NoArmor):138 ac += char.constitution.modifier139 if char.has_feature(DraconicResilience):140 if isinstance(armor, NoArmor):141 ac += 3142 if char.has_feature(Defense):143 if not isinstance(armor, NoArmor):144 ac += 1145 if char.has_feature(SoulOfTheForge):146 if isinstance(armor, HeavyArmor):147 ac += 1148 # Check if any magic items add to AC149 for mitem in char.magic_items:150 if hasattr(mitem, 'ac_bonus'):151 ac += mitem.ac_bonus152 return ac153 154class Speed():155 """156 The speed of a character157 """158 def __get__(self, char, Character):159 speed = char.race.speed160 other_speed = ''161 if isinstance(speed, str):162 other_speed = speed[2:]163 speed = int(speed[:2]) # ignore other speeds, like fly164 if char.has_feature(FastMovement):165 if not isinstance(char.armor, HeavyArmor):166 speed += 10167 if char.has_feature(SuperiorMobility):168 speed += 10169 if isinstance(char.armor, NoArmor) or (char.armor is None):170 for f in char.features:171 if isinstance(f, UnarmoredMovement):172 speed += f.speed_bonus173 if char.has_feature(GiftOfTheDepths):174 if 'swim' not in other_speed:175 other_speed += ' ({:d} swim)'.format(speed)176 if char.has_feature(SeaSoul):177 if 'swim' not in other_speed:178 other_speed += ' (30 swim)'179 return '{:d}{:s}'.format(speed, other_speed)180class Initiative():181 """A character's initiative"""182 def __get__(self, char, Character):183 ini = char.dexterity.modifier184 if char.has_feature(QuickDraw):185 ini += char.proficiency_bonus186 if char.has_feature(DreadAmbusher):187 ini += char.wisdom.modifier188 if char.has_feature(RakishAudacity):189 ini += char.charisma.modifier190 ini = '{:+d}'.format(ini)191 has_advantage = (char.has_feature(NaturalExplorerRevised) or192 char.has_feature(FeralInstinct) or193 char.has_feature(AmbushMaster))194 if has_advantage:195 ini += '(A)'196 return ini...capture.py

Source: capture.py

...11c = FPrint.Context()12c.enumerate()13devices = c.get_devices()14d = devices[0]15assert d.has_feature(FPrint.DeviceFeature.CAPTURE)16assert d.has_feature(FPrint.DeviceFeature.IDENTIFY)17assert d.has_feature(FPrint.DeviceFeature.VERIFY)18assert not d.has_feature(FPrint.DeviceFeature.DUPLICATES_CHECK)19assert not d.has_feature(FPrint.DeviceFeature.STORAGE)20assert not d.has_feature(FPrint.DeviceFeature.STORAGE_LIST)21assert not d.has_feature(FPrint.DeviceFeature.STORAGE_DELETE)22assert not d.has_feature(FPrint.DeviceFeature.STORAGE_CLEAR)23del devices24d.open_sync()25img = d.capture_sync(True)26d.close_sync()27del d28del c29width = img.get_width()30height = img.get_height()31c_img = cairo.ImageSurface(cairo.FORMAT_RGB24, width, height)32c_rowstride = c_img.get_stride()33buf = img.get_data()34c_buf = c_img.get_data()35for x in range(width):36 for y in range(height):...Blogs

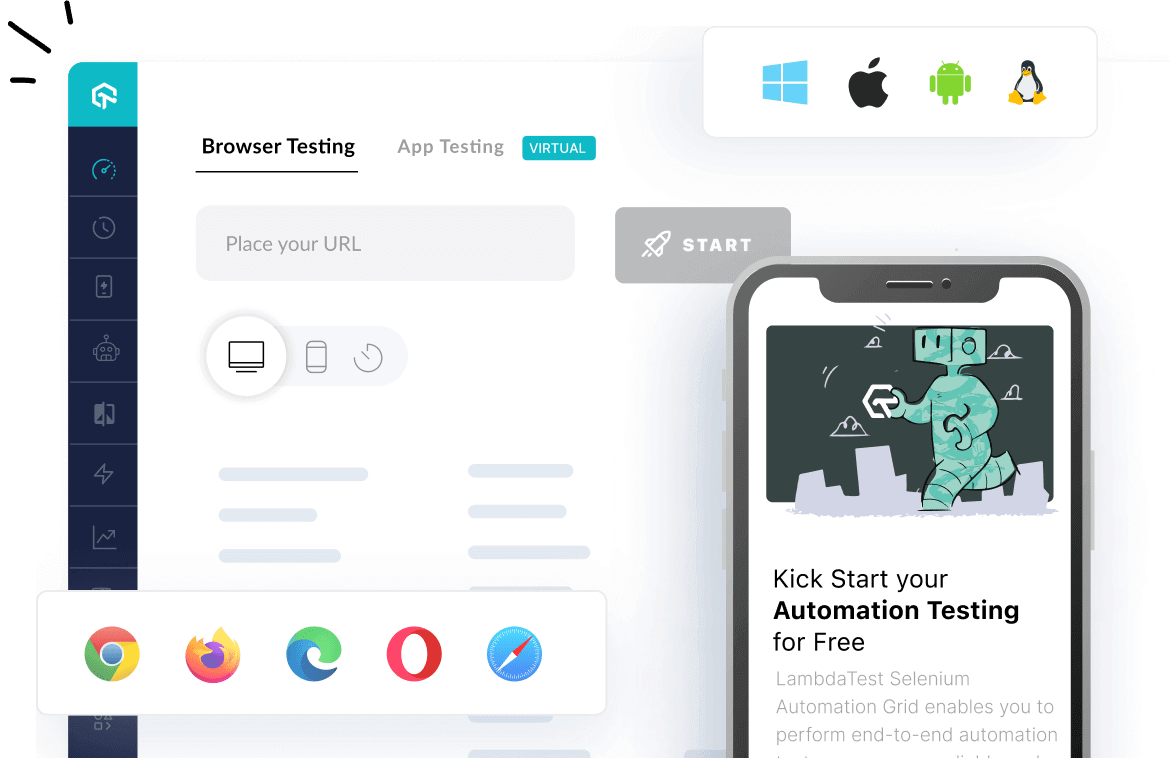

Check out the latest blogs from LambdaTest on this topic:

Automating testing is a crucial step in the development pipeline of a software product. In an agile development environment, where there is continuous development, deployment, and maintenance of software products, automation testing ensures that the end software products delivered are error-free.

Before we discuss the Joomla testing, let us understand the fundamentals of Joomla and how this content management system allows you to create and maintain web-based applications or websites without having to write and implement complex coding requirements.

The QA testing career includes following an often long, winding road filled with fun, chaos, challenges, and complexity. Financially, the spectrum is broad and influenced by location, company type, company size, and the QA tester’s experience level. QA testing is a profitable, enjoyable, and thriving career choice.

It’s strange to hear someone declare, “This can’t be tested.” In reply, I contend that everything can be tested. However, one must be pleased with the outcome of testing, which might include failure, financial loss, or personal injury. Could anything be tested when a claim is made with this understanding?

When it comes to UI components, there are two versatile methods that we can use to build it for your website: either we can use prebuilt components from a well-known library or framework, or we can develop our UI components from scratch.

Automation Testing Tutorials

Learn to execute automation testing from scratch with LambdaTest Learning Hub. Right from setting up the prerequisites to run your first automation test, to following best practices and diving deeper into advanced test scenarios. LambdaTest Learning Hubs compile a list of step-by-step guides to help you be proficient with different test automation frameworks i.e. Selenium, Cypress, TestNG etc.

LambdaTest Learning Hubs:

- JUnit Tutorial

- TestNG Tutorial

- Webdriver Tutorial

- WebDriverIO Tutorial

- Protractor Tutorial

- Selenium 4 Tutorial

- Jenkins Tutorial

- NUnit Tutorial

- Jest Tutorial

- Playwright Tutorial

- Cypress Tutorial

- PyTest Tutorial

YouTube

You could also refer to video tutorials over LambdaTest YouTube channel to get step by step demonstration from industry experts.

Try LambdaTest Now !!

Get 100 minutes of automation test minutes FREE!!