How to use check_frame method in Airtest

Best Python code snippet using Airtest

test_fpga_core.py

Source: test_fpga_core.py

1#!/usr/bin/env python2"""3Copyright (c) 2015-2018 Alex Forencich4Permission is hereby granted, free of charge, to any person obtaining a copy5of this software and associated documentation files (the "Software"), to deal6in the Software without restriction, including without limitation the rights7to use, copy, modify, merge, publish, distribute, sublicense, and/or sell8copies of the Software, and to permit persons to whom the Software is9furnished to do so, subject to the following conditions:10The above copyright notice and this permission notice shall be included in11all copies or substantial portions of the Software.12THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR13IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY14FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE15AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER16LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,17OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN18THE SOFTWARE.19"""20from myhdl import *21import os22import eth_ep23import arp_ep24import udp_ep25import rgmii_ep26module = 'fpga_core'27testbench = 'test_%s' % module28srcs = []29srcs.append("../rtl/%s.v" % module)30srcs.append("../lib/eth/rtl/iddr.v")31srcs.append("../lib/eth/rtl/oddr.v")32srcs.append("../lib/eth/rtl/ssio_ddr_in.v")33srcs.append("../lib/eth/rtl/ssio_ddr_out.v")34srcs.append("../lib/eth/rtl/rgmii_phy_if.v")35srcs.append("../lib/eth/rtl/eth_mac_1g_rgmii_fifo.v")36srcs.append("../lib/eth/rtl/eth_mac_1g_rgmii.v")37srcs.append("../lib/eth/rtl/eth_mac_1g.v")38srcs.append("../lib/eth/rtl/axis_gmii_rx.v")39srcs.append("../lib/eth/rtl/axis_gmii_tx.v")40srcs.append("../lib/eth/rtl/ve_lfsr.v")41srcs.append("../lib/eth/rtl/eth_axis_rx.v")42srcs.append("../lib/eth/rtl/eth_axis_tx.v")43srcs.append("../lib/eth/rtl/udp_complete.v")44srcs.append("../lib/eth/rtl/udp_checksum_gen.v")45srcs.append("../lib/eth/rtl/udp.v")46srcs.append("../lib/eth/rtl/udp_ip_rx.v")47srcs.append("../lib/eth/rtl/udp_ip_tx.v")48srcs.append("../lib/eth/rtl/ip_complete.v")49srcs.append("../lib/eth/rtl/ip.v")50srcs.append("../lib/eth/rtl/ip_eth_rx.v")51srcs.append("../lib/eth/rtl/ip_eth_tx.v")52srcs.append("../lib/eth/rtl/ip_arb_mux.v")53srcs.append("../lib/eth/rtl/arp.v")54srcs.append("../lib/eth/rtl/arp_cache.v")55srcs.append("../lib/eth/rtl/arp_eth_rx.v")56srcs.append("../lib/eth/rtl/arp_eth_tx.v")57srcs.append("../lib/eth/rtl/eth_arb_mux.v")58srcs.append("../lib/eth/lib/axis/rtl/arbiter.v")59srcs.append("../lib/eth/lib/axis/rtl/priority_encoder.v")60srcs.append("../lib/eth/lib/axis/rtl/axis_fifo.v")61srcs.append("../lib/eth/lib/axis/rtl/axis_async_fifo.v")62srcs.append("../lib/eth/lib/axis/rtl/axis_async_fifo_adapter.v")63srcs.append("%s.v" % testbench)64src = ' '.join(srcs)65build_cmd = "iverilog -o %s.vvp %s" % (testbench, src)66def bench():67 # Parameters68 TARGET = "SIM"69 # Inputs70 clk = Signal(bool(0))71 rst = Signal(bool(0))72 clk_125mhz = Signal(bool(0))73 clk90_125mhz = Signal(bool(0))74 rst_125mhz = Signal(bool(0))75 current_test = Signal(intbv(0)[8:])76 btnu = Signal(bool(0))77 btnl = Signal(bool(0))78 btnd = Signal(bool(0))79 btnr = Signal(bool(0))80 btnc = Signal(bool(0))81 sw = Signal(intbv(0)[8:])82 phy_rx_clk = Signal(bool(0))83 phy_rxd = Signal(intbv(0)[4:])84 phy_rx_ctl = Signal(bool(0))85 uart_txd = Signal(bool(0))86 uart_rts = Signal(bool(0))87 # Outputs88 ledu = Signal(bool(0))89 ledl = Signal(bool(0))90 ledd = Signal(bool(0))91 ledr = Signal(bool(0))92 ledc = Signal(bool(0))93 led = Signal(intbv(0)[8:])94 phy_tx_clk = Signal(bool(0))95 phy_txd = Signal(intbv(0)[4:])96 phy_tx_ctl = Signal(bool(0))97 phy_reset_n = Signal(bool(0))98 uart_rxd = Signal(bool(0))99 uart_cts = Signal(bool(0))100 # sources and sinks101 mii_select = Signal(bool(0))102 rgmii_source = rgmii_ep.RGMIISource()103 rgmii_source_logic = rgmii_source.create_logic(104 phy_rx_clk,105 rst,106 txd=phy_rxd,107 tx_ctl=phy_rx_ctl,108 mii_select=mii_select,109 name='rgmii_source'110 )111 rgmii_sink = rgmii_ep.RGMIISink()112 rgmii_sink_logic = rgmii_sink.create_logic(113 phy_tx_clk,114 rst,115 rxd=phy_txd,116 rx_ctl=phy_tx_ctl,117 mii_select=mii_select,118 name='rgmii_sink'119 )120 # DUT121 if os.system(build_cmd):122 raise Exception("Error running build command")123 dut = Cosimulation(124 "vvp -m myhdl %s.vvp -lxt2" % testbench,125 clk_125mhz=clk_125mhz,126 clk90_125mhz=clk90_125mhz,127 rst_125mhz=rst_125mhz,128 current_test=current_test,129 btnu=btnu,130 btnl=btnl,131 btnd=btnd,132 btnr=btnr,133 btnc=btnc,134 sw=sw,135 ledu=ledu,136 ledl=ledl,137 ledd=ledd,138 ledr=ledr,139 ledc=ledc,140 led=led,141 phy_rx_clk=phy_rx_clk,142 phy_rxd=phy_rxd,143 phy_rx_ctl=phy_rx_ctl,144 phy_tx_clk=phy_tx_clk,145 phy_txd=phy_txd,146 phy_tx_ctl=phy_tx_ctl,147 phy_reset_n=phy_reset_n,148 uart_rxd=uart_rxd,149 uart_txd=uart_txd,150 uart_rts=uart_rts,151 uart_cts=uart_cts152 )153 @always(delay(4))154 def clkgen():155 clk.next = not clk156 clk_125mhz.next = not clk_125mhz157 @instance158 def clkgen2():159 yield delay(4+2)160 while True:161 clk90_125mhz.next = not clk90_125mhz162 yield delay(4)163 rx_clk_hp = Signal(int(4))164 @instance165 def rx_clk_gen():166 while True:167 yield delay(int(rx_clk_hp))168 phy_rx_clk.next = not phy_rx_clk169 @instance170 def check():171 yield delay(100)172 yield clk.posedge173 rst.next = 1174 rst_125mhz.next = 1175 yield clk.posedge176 rst.next = 0177 rst_125mhz.next = 0178 yield clk.posedge179 yield delay(100)180 yield clk.posedge181 # testbench stimulus182 yield clk.posedge183 print("test 1: test UDP RX packet")184 current_test.next = 1185 test_frame = udp_ep.UDPFrame()186 test_frame.eth_dest_mac = 0x020000000000187 test_frame.eth_src_mac = 0xDAD1D2D3D4D5188 test_frame.eth_type = 0x0800189 test_frame.ip_version = 4190 test_frame.ip_ihl = 5191 test_frame.ip_dscp = 0192 test_frame.ip_ecn = 0193 test_frame.ip_length = None194 test_frame.ip_identification = 0195 test_frame.ip_flags = 2196 test_frame.ip_fragment_offset = 0197 test_frame.ip_ttl = 64198 test_frame.ip_protocol = 0x11199 test_frame.ip_header_checksum = None200 test_frame.ip_source_ip = 0xc0a80181201 test_frame.ip_dest_ip = 0xc0a80180202 test_frame.udp_source_port = 5678203 test_frame.udp_dest_port = 1234204 test_frame.payload = bytearray(range(32))205 test_frame.build()206 rgmii_source.send(b'\x55\x55\x55\x55\x55\x55\x55\xD5'+test_frame.build_eth().build_axis_fcs().data)207 # wait for ARP request packet208 while rgmii_sink.empty():209 yield clk.posedge210 rx_frame = rgmii_sink.recv()211 check_eth_frame = eth_ep.EthFrame()212 check_eth_frame.parse_axis_fcs(rx_frame.data[8:])213 check_frame = arp_ep.ARPFrame()214 check_frame.parse_eth(check_eth_frame)215 print(check_frame)216 assert check_frame.eth_dest_mac == 0xFFFFFFFFFFFF217 assert check_frame.eth_src_mac == 0x020000000000218 assert check_frame.eth_type == 0x0806219 assert check_frame.arp_htype == 0x0001220 assert check_frame.arp_ptype == 0x0800221 assert check_frame.arp_hlen == 6222 assert check_frame.arp_plen == 4223 assert check_frame.arp_oper == 1224 assert check_frame.arp_sha == 0x020000000000225 assert check_frame.arp_spa == 0xc0a80180226 assert check_frame.arp_tha == 0x000000000000227 assert check_frame.arp_tpa == 0xc0a80181228 # generate response229 arp_frame = arp_ep.ARPFrame()230 arp_frame.eth_dest_mac = 0x020000000000231 arp_frame.eth_src_mac = 0xDAD1D2D3D4D5232 arp_frame.eth_type = 0x0806233 arp_frame.arp_htype = 0x0001234 arp_frame.arp_ptype = 0x0800235 arp_frame.arp_hlen = 6236 arp_frame.arp_plen = 4237 arp_frame.arp_oper = 2238 arp_frame.arp_sha = 0xDAD1D2D3D4D5239 arp_frame.arp_spa = 0xc0a80181240 arp_frame.arp_tha = 0x020000000000241 arp_frame.arp_tpa = 0xc0a80180242 rgmii_source.send(b'\x55\x55\x55\x55\x55\x55\x55\xD5'+arp_frame.build_eth().build_axis_fcs().data)243 while rgmii_sink.empty():244 yield clk.posedge245 rx_frame = rgmii_sink.recv()246 check_eth_frame = eth_ep.EthFrame()247 check_eth_frame.parse_axis_fcs(rx_frame.data[8:])248 check_frame = udp_ep.UDPFrame()249 check_frame.parse_eth(check_eth_frame)250 print(check_frame)251 assert check_frame.eth_dest_mac == 0xDAD1D2D3D4D5252 assert check_frame.eth_src_mac == 0x020000000000253 assert check_frame.eth_type == 0x0800254 assert check_frame.ip_version == 4255 assert check_frame.ip_ihl == 5256 assert check_frame.ip_dscp == 0257 assert check_frame.ip_ecn == 0258 assert check_frame.ip_identification == 0259 assert check_frame.ip_flags == 2260 assert check_frame.ip_fragment_offset == 0261 assert check_frame.ip_ttl == 64262 assert check_frame.ip_protocol == 0x11263 assert check_frame.ip_source_ip == 0xc0a80180264 assert check_frame.ip_dest_ip == 0xc0a80181265 assert check_frame.udp_source_port == 1234266 assert check_frame.udp_dest_port == 5678267 assert check_frame.payload.data == bytearray(range(32))268 assert rgmii_source.empty()269 assert rgmii_sink.empty()270 yield delay(100)271 raise StopSimulation272 return instances()273def test_bench():274 sim = Simulation(bench())275 sim.run()276if __name__ == '__main__':277 print("Running test...")...pyunit_frame_slicing3.py

Source: pyunit_frame_slicing3.py

...11 [16, -5, 12],12 [32, -6, 99],13 [64, -7, 1],14 ], column_names=["a", "b", "c"])15 check_frame(fr[::2, :], [[1, -1, 0], [4, -3, 50], [16, -5, 12], [64, -7, 1]])16 check_frame(fr[1:3, :2], [[2, -2], [4, -3]])17 check_frame(fr[:100, 1], [[-1], [-2], [-3], [-4], [-5], [-6], [-7]])18 check_frame(fr[:, 1], [[-1], [-2], [-3], [-4], [-5], [-6], [-7]])19 check_frame(fr[-2:, :], [[32, -6, 99], [64, -7, 1]])20 check_frame(fr[-3:-1, -1:], [[12], [99]])21 check_frame(fr[-10:-6, :], [[1, -1, 0]])22 # check_frame(fr[-3::2, ::2], [[16, 12], [64, 1]])23 fr[:, 1] = 024 check_frame(fr[:, 1], [[0]] * 7)25def check_frame(actual, expected):26 exp_shape = (len(expected), len(expected[0]))27 assert actual.shape == exp_shape, "Incorrect frame size: actual = %r vs expected = %r" % (actual.shape, exp_shape)28 data = [[int(e) for e in row]29 for row in actual.as_data_frame(False, False)]30 assert actual.shape == exp_shape, "Incorrect frame size: actual = %r vs expected = %r" % (actual.shape, exp_shape)31 assert data == expected, "Frames do not coincide:\nActual: %r\nExpected: %r\n" % (data, expected)32if __name__ == "__main__":33 h2o.init()...Blogs

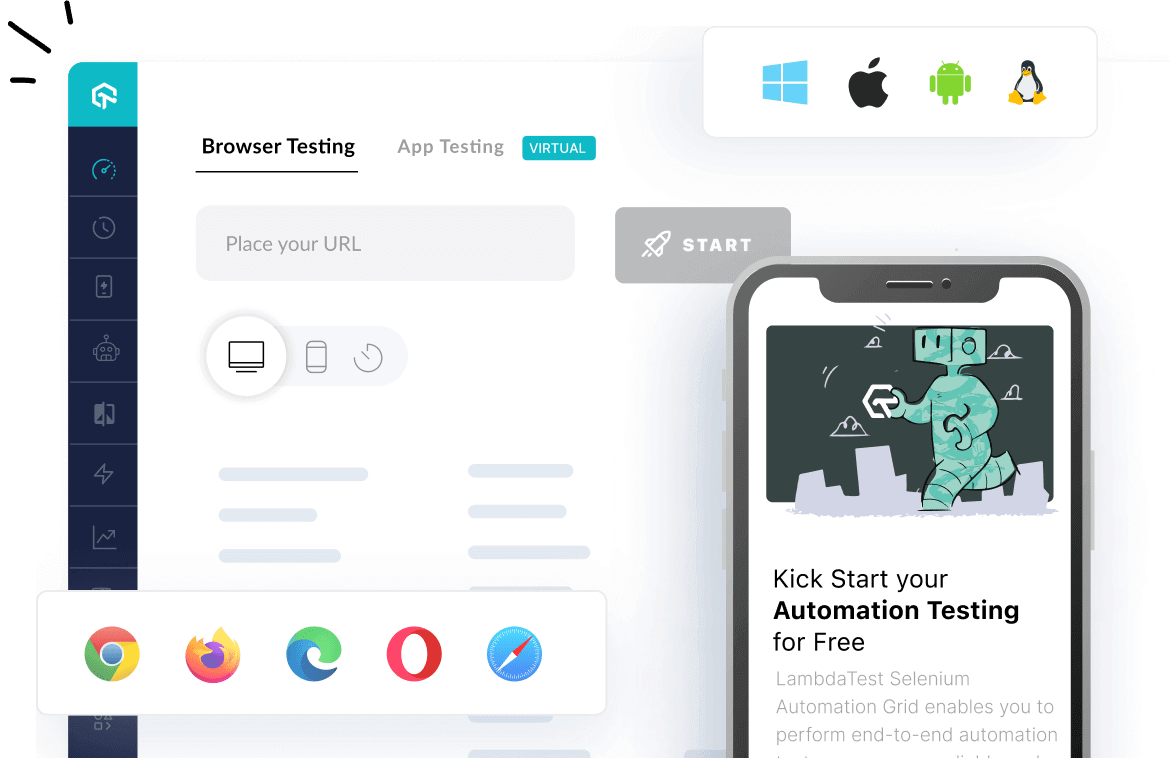

Check out the latest blogs from LambdaTest on this topic:

Unit testing is typically software testing within the developer domain. As the QA role expands in DevOps, QAOps, DesignOps, or within an Agile team, QA testers often find themselves creating unit tests. QA testers may create unit tests within the code using a specified unit testing tool, or independently using a variety of methods.

People love to watch, read and interact with quality content — especially video content. Whether it is sports, news, TV shows, or videos captured on smartphones, people crave digital content. The emergence of OTT platforms has already shaped the way people consume content. Viewers can now enjoy their favorite shows whenever they want rather than at pre-set times. Thus, the OTT platform’s concept of viewing anything, anytime, anywhere has hit the right chord.

Agile project management is a great alternative to traditional methods, to address the customer’s needs and the delivery of business value from the beginning of the project. This blog describes the main benefits of Agile for both the customer and the business.

The purpose of developing test cases is to ensure the application functions as expected for the customer. Test cases provide basic application documentation for every function, feature, and integrated connection. Test case development often detects defects in the design or missing requirements early in the development process. Additionally, well-written test cases provide internal documentation for all application processing. Test case development is an important part of determining software quality and keeping defects away from customers.

I routinely come across test strategy documents when working with customers. They are lengthy—100 pages or more—and packed with monotonous text that is routinely reused from one project to another. Yawn once more— the test halt and resume circumstances, the defect management procedure, entrance and exit criteria, unnecessary generic risks, and in fact, one often-used model replicates the requirements of textbook testing, from stress to systems integration.

Automation Testing Tutorials

Learn to execute automation testing from scratch with LambdaTest Learning Hub. Right from setting up the prerequisites to run your first automation test, to following best practices and diving deeper into advanced test scenarios. LambdaTest Learning Hubs compile a list of step-by-step guides to help you be proficient with different test automation frameworks i.e. Selenium, Cypress, TestNG etc.

LambdaTest Learning Hubs:

- JUnit Tutorial

- TestNG Tutorial

- Webdriver Tutorial

- WebDriverIO Tutorial

- Protractor Tutorial

- Selenium 4 Tutorial

- Jenkins Tutorial

- NUnit Tutorial

- Jest Tutorial

- Playwright Tutorial

- Cypress Tutorial

- PyTest Tutorial

YouTube

You could also refer to video tutorials over LambdaTest YouTube channel to get step by step demonstration from industry experts.

Try LambdaTest Now !!

Get 100 minutes of automation test minutes FREE!!